估值之家

随着近期台积电发布2025Q4业绩,A股与SiC(碳化硅)相关的股票纷纷大涨,期间伴随着诸多SiC作为台积电核心映射的“小作文”,包括但不限于天岳先进(02631.HK、688234.SH)A股20厘米涨停、三安光电(600703.SH)、宇晶股份(002943.SZ)等公司10厘米涨停,晶升股份(688478.SH)、晶盛机电(300316.SZ)等也纷纷大涨。

然而有趣的是,无论是在台积电2025Q4的财报中还是Earnings Call中,以CoWoS或SiC作为关键词,搜索结果都是零。

图片说明:天岳先进A股20厘米涨停、港股大涨13.50%,数据来源于Wind

熟悉二级市场的投资者最清楚不过,每当一个“新”的题材或“新”的逻辑出现时,你首先要做的不是去求证,而是先信了再说,然后等拉高后再卖给后信的人,如果你的第一想法是去求证真伪,或许你就已经输在起跑线上了。

然而,估值之家作为一家风格比较严谨的研究机构,更愿意去尝试探讨事件的真相,一方面期望能带给专业投资者一定参考价值,另一方面也期望普通投资者不去踩坑。

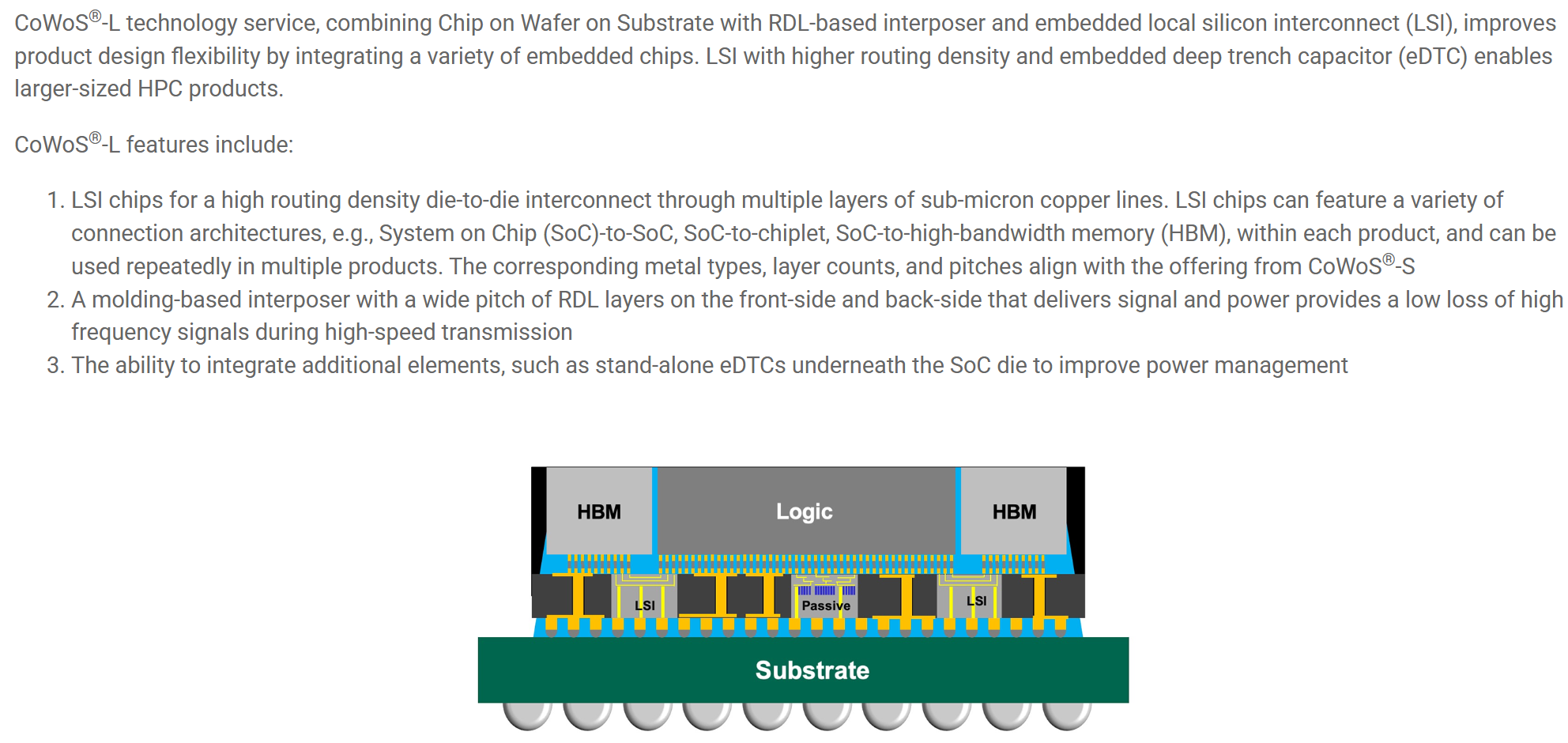

CoWoS先进封装工艺简介

CoWoS是Chip on Wafer on Substrate的缩写,是台积电独家开发的一种类似于“三明治结构的”2.5D先进封装工艺,指先把Chip芯片(如逻辑芯片GPU和存储芯片HBM)封装到Wafer晶圆(中间这一层被称为中介层Interposer)表面上,即CoW,然后再把CoW封装在Substrate基板上,即oS,最后封装基板负责将整个模块连接到主板(PCB)上,合起来称作CoWoS,中文可以翻译为“晶圆级封装工艺”。

在AI爆发之前,市场并不太关心封装工艺,但AI训练和推理都需要海量数据,传统的计算架构中,内存距离GPU太远、速度太慢,台积电开发的CoWoS工艺允许将HBM直接紧贴着GPU放在同一个中介层Interposer上,极大地缩短传输距离并提升了带宽。

图片说明:CoWoS工艺结构示意图,数据来源于GitHub

根据中介层Interposer所采用材料的不同,台积电将CoWoS分为三类,第一类是CoWoS-S,其中S代表Silicon,指中介层使用全硅晶圆,是最早应用于AI算力的方案,如英伟达H100采用的便是CoWoS-S。

图片说明:CoWoS-S工艺结构示意图,数据来源于台积电

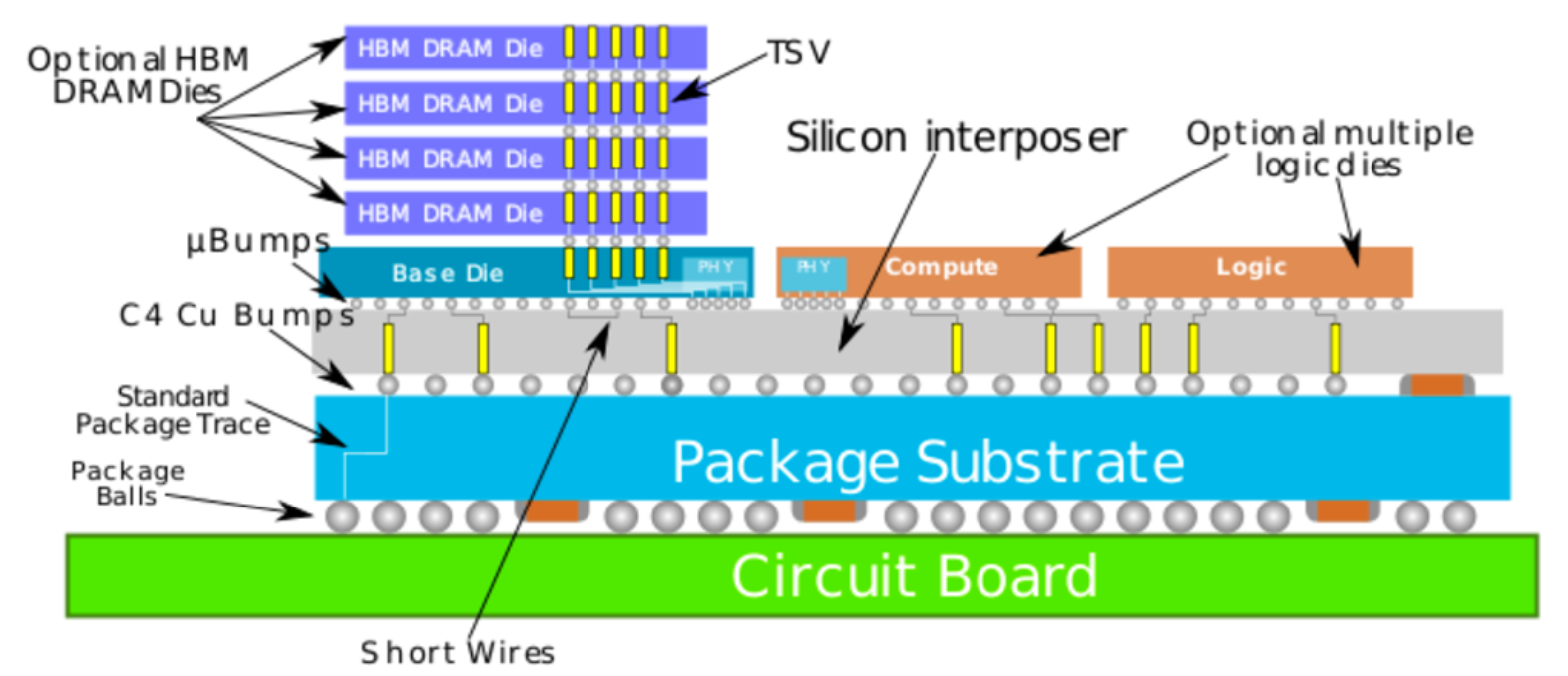

第二类是CoWoS-R,其中R代表Redistribution Layer,指重新布线层,在中介层中使用了更便宜的有机聚合物来替代无机硅材料,是InFO(扇型封装)工艺的一种延伸,主要应用于交换机ASIC芯片、部分推理芯片等。

图片说明:CoWoS-R工艺结构示意图,数据来源于台积电

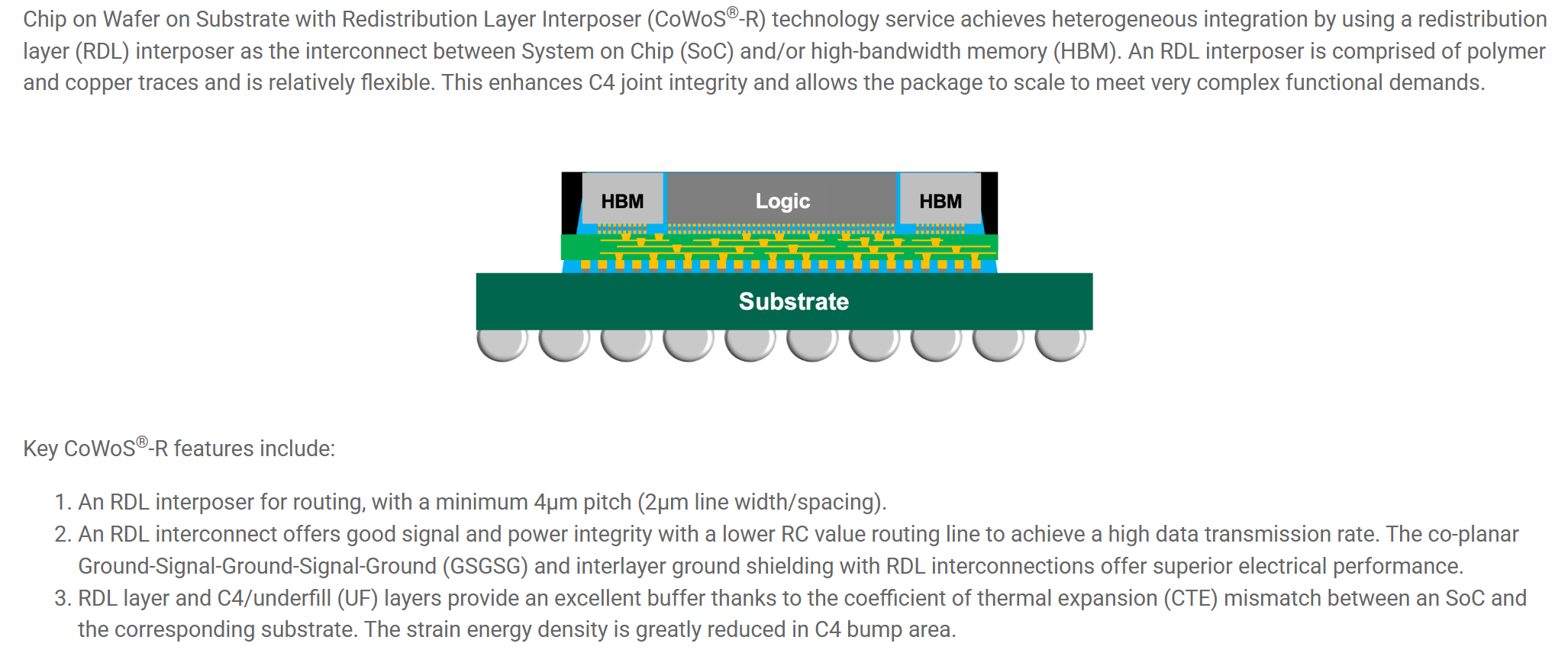

第三类是CoWoS-L,其中L代表Local Silicon Interconnect,指局部硅互联,是CoWoS-S(全硅)和 CoWoS-R(有机)的“混血儿”,结合了无机硅的高密度互连优势和有机材料的大尺寸和低成本优势,是支持超大尺寸封装AI芯片(如英伟达Blackwell GB200)的必选项。

图片说明:CoWoS-L工艺结构示意图,数据来源于台积电

需要特别说明的是,除CoWoS-S、CoWoS-R、CoWoS-L外(对应中介层Interposer材料分别为全硅、有机物、硅和有机物混合),台积电目前尚未对外公开表示有新的工艺,甚至也没有对外传递出要采用新工艺的计划或风声。

“小作文”中关于SiC导入CoWoS的逻辑梳理

在台积电2025Q4财报发布后,市场上出现了多篇关于SiC将成为下一代CoWoS中介层Interposer材料的“小作文”,就拿估值之家看到的来说,至少有不少于三家券商给出了关于SiC结论性的推荐,如“SiC有望成为CoWoS中的新一代核心材料”、“SiC有望在2027年应用于英伟达新一代Rubin芯片中” 等等。

图片说明:关于SiC推票“小作文”,数据来源于某券商

梳理市面上关于SiC的“小作文”,虽然论据略有差别,但结论大同小异,一般来说有以下几个共同点:

第一,结论先行,且结论相当笃定。例如认为台积电采用SiC作为CoWoS中介层Interposer的材料,基本已是确定性趋势,且市场空间非常之大。

图片说明:关于论证SiC作为CoWoS下一代中介层Interposer材料的结论相当笃定,数据来源于某券商

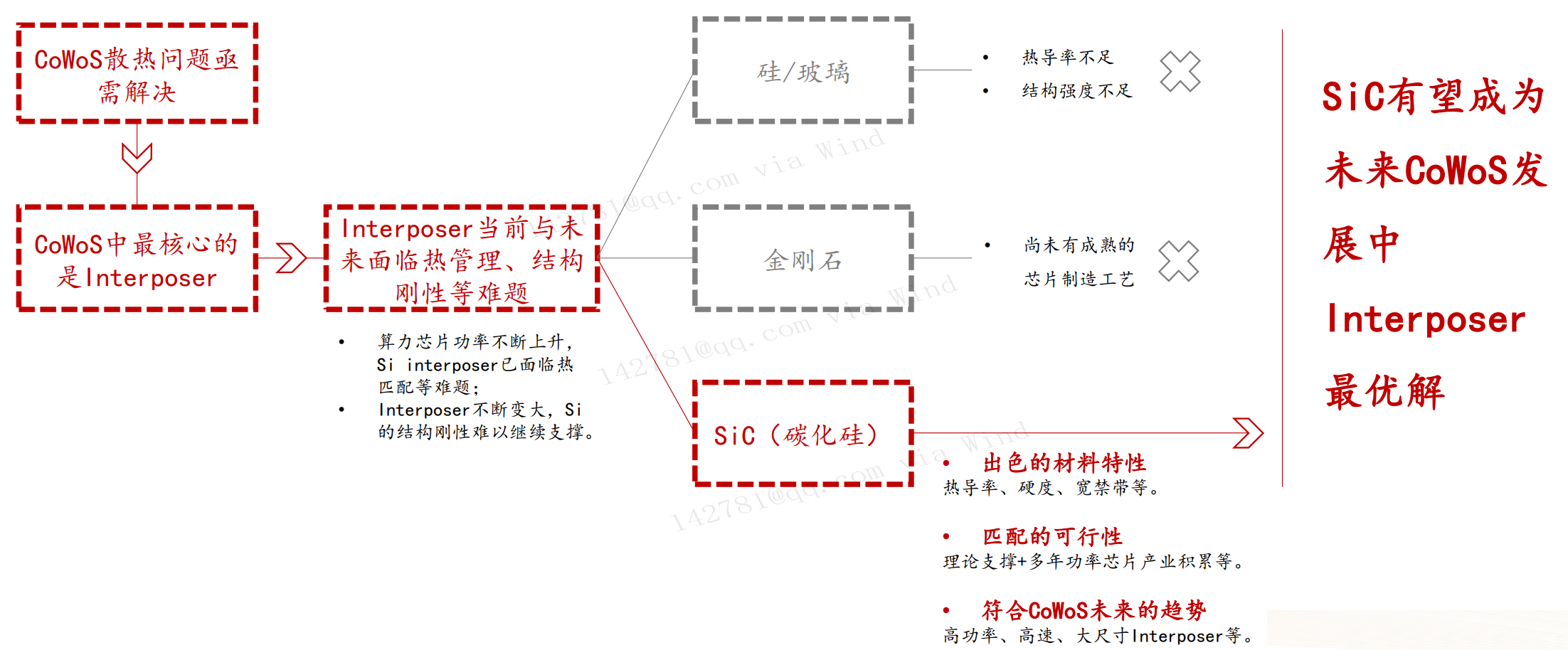

第二,逻辑看起来非常顺,但却不容易证伪。例如首先将原来CoWoS-S和CoWoS-L方案中的缺点一一列举,然后再说明SiC的优点,正好可以弥补原方案中的缺点。

例如,讲硅的热导率不足,硅的热导率约为130 W/(m·K),在处理普通处理器时绰绰有余,但在面对如今动辄几百瓦甚至上千瓦功耗的AI芯片时,硅如同一个“闷罐”,导致热堆积更加严重。而SiC具备极致的散热能力,SiC的热导率高达490~500W/(m·K),是硅材料的近4倍,更是玻璃基板(约1~5 W/(m·K))的百倍以上,这意味着在同样的功耗下,SiC能以更快的速度将热量导出,解决热堆积的核心痛点。

例如,讲硅的莫氏硬度不足,硅的莫氏硬度约为7,机械强度相对较弱,当巨大的热量产生热应力时,硅中介层极易发生翘曲,为了应对这个问题台积电曾尝试从CoWoS-S转向CoWoS-L,试图通过做小连接面积来牺牲部分性能以实现量产,然而即便使用了CoWoS-L,在英伟达Blackwell系列芯片中翘曲问题依然存在。而SiC具备优异的机械性能,SiC的莫氏硬度高达9.5,仅次于金刚石,远高于硅,这种极高的硬度意味着更好的刚性,能够在高热应力环境下保持形态稳定,大幅减少翘曲和裂纹的发生,从而直接提升封装良率。

图片说明:关于论证CoWoS原方案的缺点以及SiC优点的“小作文”,数据来源于某券商

第三,并未给出严格的数据出处,尤其是缺乏非常权威的数据出处(比如台积电和英伟达是否有相关表述或指引)。例如,论证SiC作为CoWoS下一代中介层Interposer材料的证据时,往往采用第三方的结论,而非更权威的出处。

例如,部分券商根据北京大学、Nature、一些实验室团队的相关论文,验证了当前的硅和玻璃在材料特性上不及SiC与金刚石,而金刚石仍难以匹配芯片制造工艺,因此给出判断,因为SiC在性能与可行性两方面的优势,有望成为未来CoWoS interposer的最适宜替代材料。

图片说明:关于论证SiC作为CoWoS下一代中介层Interposer材料的证据时,采用第三方的结论,数据来源于某券商

信誓旦旦的“小作文”,逻辑真的有那么硬吗?

首先,估值之家并非台积电内部人士、也非英伟达内部人士,无法像“小作文”一样给出一个笃定或信誓旦旦的结论;其次,虽然缺乏非常明确的结论,但估值之家可以通过对公开资料的深度研究,来发出合理的质疑声,以期给投资者带来一定的参考价值。

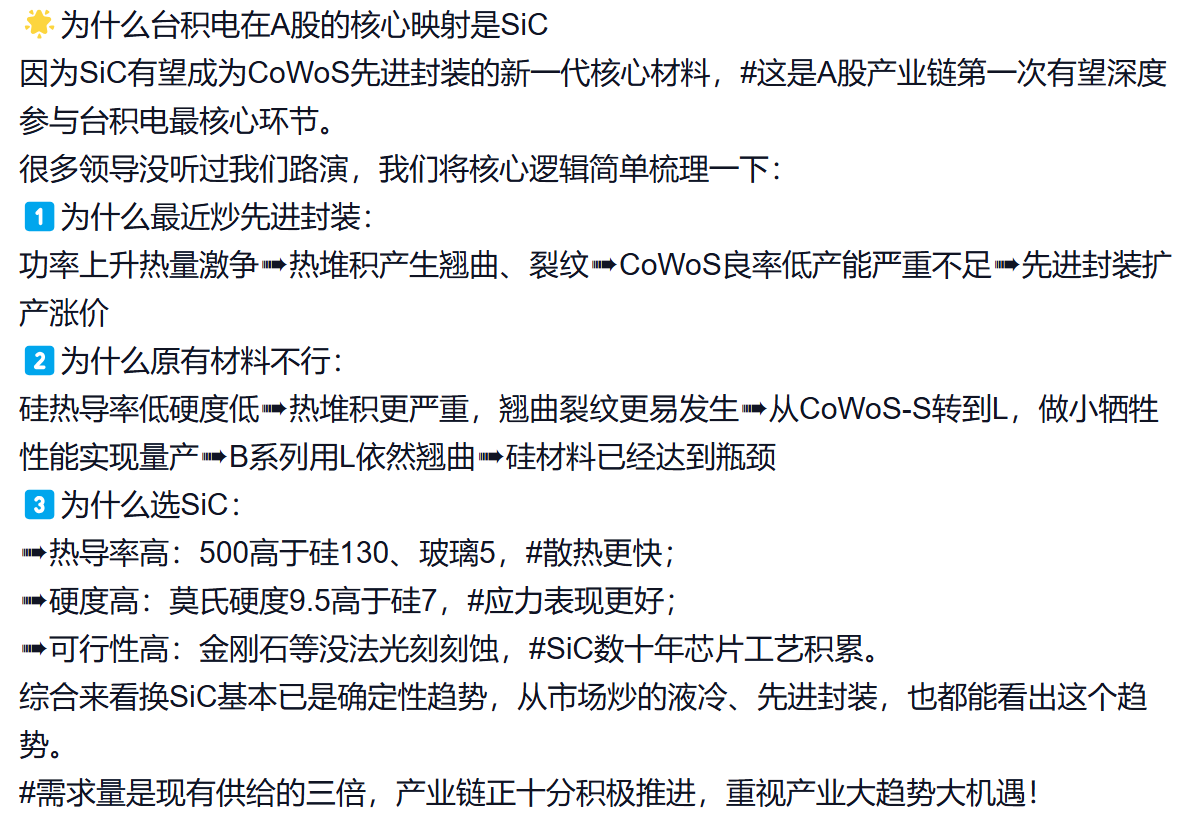

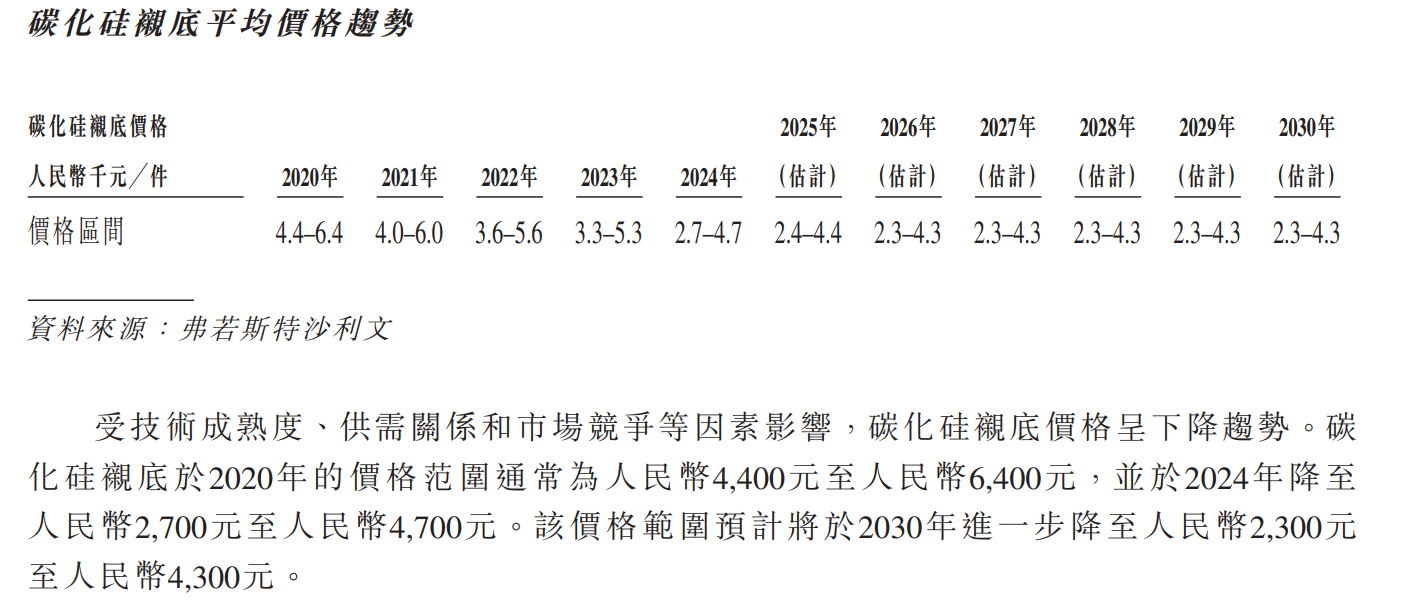

第一,SiC晶圆的成本远远高于硅晶圆,用SiC作为CoWoS的中介层Interposer,是否符合产业的中长期发展趋势?从台积电过去CoWoS工艺发展方向上看,从CoWoS-S到CoWoS-R再到CoWoS-L,台积电总是朝着成本更低的方向努力。而SiC即便近年来价格下降非常显著,但仍有2700~4700元/片左右,相比于8英寸普通硅晶圆的价格区间,超出至少10倍不止。

图片说明:2024年SiC晶圆的单价约2700~4700元/片,数据来源于天岳先进港股招股书

第二,晶圆尺寸是错配的。台积电的CoWoS生产线完全基于12英寸(300mm)晶圆厂设备,目前的AI芯片加上HBM,封装后的尺寸非常大,必须用12英寸晶圆才能切割出足够数量的中介层Interposer,或者直接进行晶圆级键合。而目前全球SiC产业主流仍是6英寸(150mm),正在逐步开始向8英寸(200mm)起量,12英寸SiC晶圆还正处在样品研发或产业化初期阶段。这意味着,如果台积电要用SiC做CoWoS中介层Interposer,可能面临“巧妇难为无米之炊”的困境,这在工业逻辑上可能是不成立的。

图片说明:12英寸SiC晶圆的产业化进展情况,数据来源于天岳先进港股招股书

第三,在SiC上大规模制造高深宽比的TSV(硅通孔),其成本和时间消耗是硅的“数十倍甚至上百倍”,这在工业逻辑上或许不具备现实可行性。TSV作为CoWoS的核心技术,需要在中介层Interposer上打出成千上万个微小的垂直孔,而SiC的硬度莫氏为9.5(仅次于金刚石),且化学性质极度稳定,在SiC上刻蚀高深宽比的TSV极其困难、速度极慢、且非常耗费钻头和耗材。

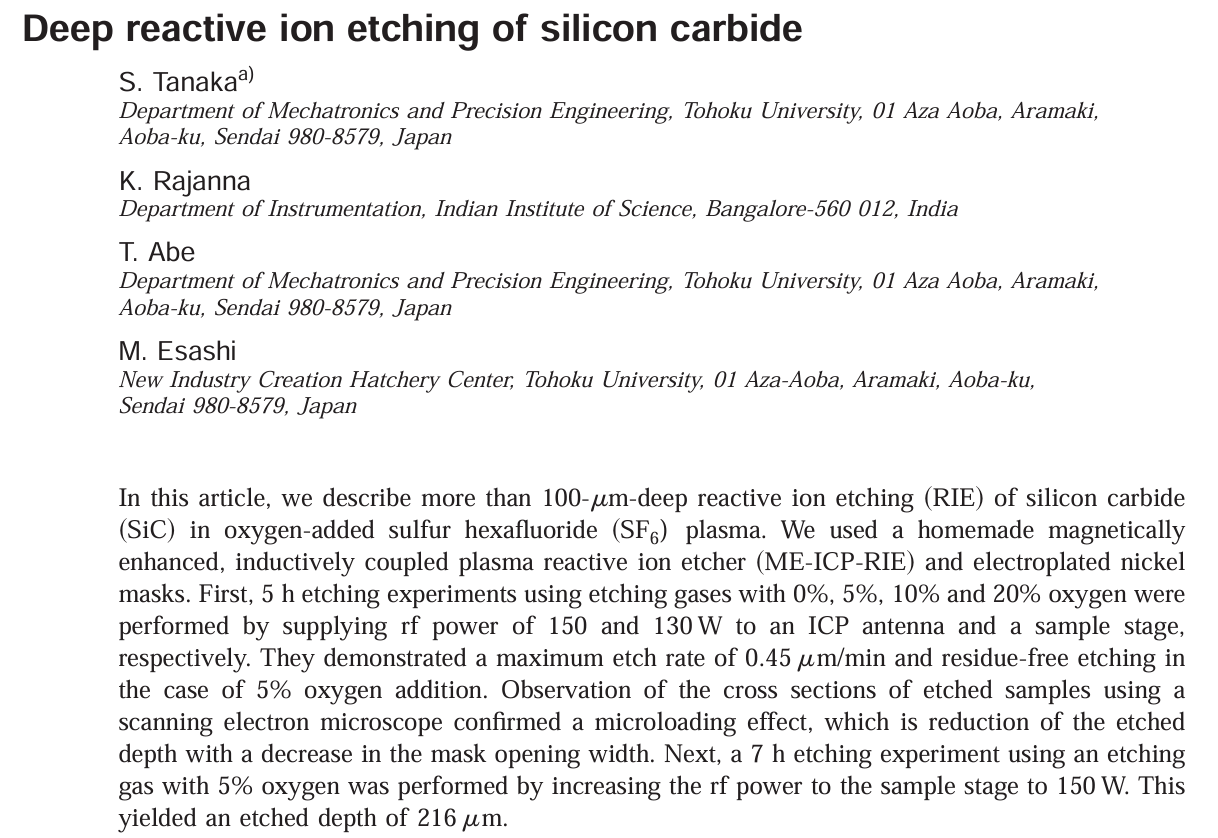

例如,NASA & IEEE Conference曾于Journal of Vacuum Science & Technology B发表文章《Deep Reactive Ion Etching of Silicon Carbide》,文章摘要中明确指出,在优化的SF6/O2等离子体环境下,SiC的最大蚀刻速率约为每分钟0.45m,同时在论文中指出,标准硅的DRIE蚀刻速率通常不低于每分钟20 m甚至更高。

换句话说,在SiC打孔工艺没有显著进步的情况下,同样是在晶圆上打一个深度为100m的TSV通孔,普通硅晶圆只需要5~10分钟,而SiC晶圆可能需要200~500分钟,这意味着一台蚀刻机一天可能最多只能处理几片SiC晶圆,而处理硅晶圆可以达到数百片,这种产能效率的差异直接导致成本差异是“数十倍甚至上百倍”量级的。

图片说明:SiC的刻蚀速率与普通硅差距约44倍,数据来源于《Deep Reactive Ion Etching of Silicon Carbide》

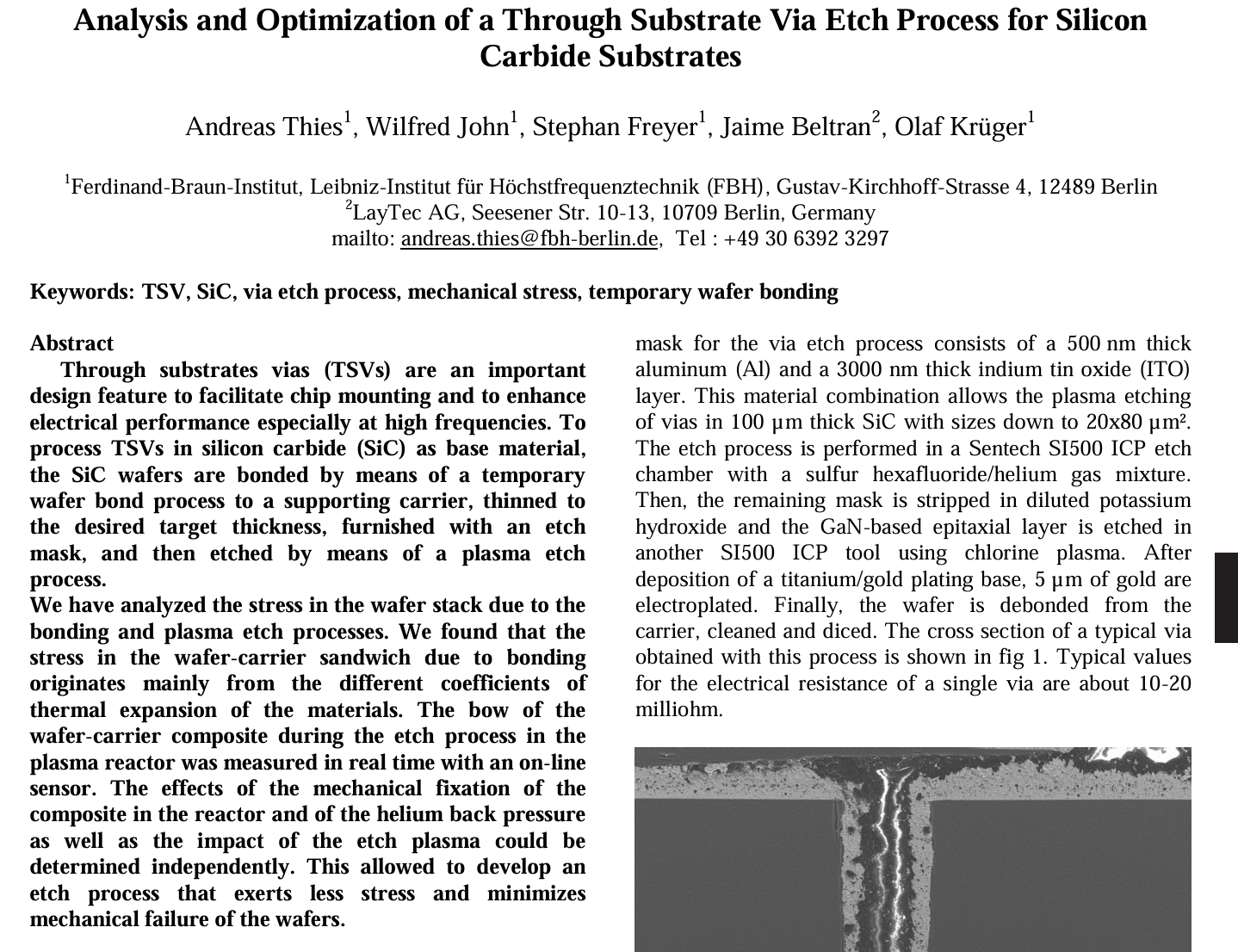

再例如,根据德国莱布尼茨研究所的论文《Analysis and Optimization of a Through Substrate Via Etch Process for Silicon Carbide Substrates》,SiC的莫氏硬度高达9.5,且化学性质呈惰性,这意味着普通的光刻胶无法承受长时间的等离子轰击,进而必须使用镍或其他金属作为硬掩膜版,从而意味着在蚀刻TSV通孔之前,还需要额外的沉积金属、光刻金属、蚀刻金属等工序,这不仅增加了耗材成本,还大幅增加了工艺流程的长度和良率风险。

图片说明:在SiC上打TSV通孔,工艺复杂度显著提高,数据来源于德国莱布尼茨研究所

最后,目前已无从考证“用SiC作为下一代CoWoS的Interposer”,这一论断的源头来自何处,即便估值之家对此论断在逻辑上充满了质疑,却仍然无法完全证伪这一论断,但估值之家还是要提醒投资者,搞不懂的可以不做,最好还是不要轻易相信“小作文”。

用户在证星号发表的信息将由本网站记录保存,仅代表作者个人观点,与本网站立场无关,不构成投资建议,据此操作风险自担